### **B TECH IN**

## ELECTRONICS (VLSI DESIGN & TECHNOLOGY) SEMESTER 3

| SLOT     | COURSE<br>NO. | COURSES                                                     | L-T-P   | HOURS | CREDITS |

|----------|---------------|-------------------------------------------------------------|---------|-------|---------|

| А        | MAT201        | PARTIAL<br>DIFFERENTIAL<br>EQUATION AND<br>COMPLEX ANALYSIS | 3-1-0   | 4     | 4       |

| В        | ECT201        | SOLID STATE DEVICE                                          | S 3-1-0 | 4     | 4       |

| С        | ECT 203       | LOGIC CIRCUIT<br>DESIGN                                     | 3-1-0   | 4     | 4       |

| D        | ECT205        | NETWORK THEORY                                              | 3-1-0   | 4     | 4       |

| E<br>1/2 | EST200        | DESIGN AND<br>ENGINEERING                                   | 2-0-0   | 2     | 2       |

|          | HUT200        | PROFESSIONAL<br>ETHICS                                      | 2-0-0   | 2     | 2       |

| F        | MCN201        | SUSTAINABLE<br>ENGINEERING                                  | 2-0-0   | 2     | -       |

| S        | ECL 201       | SCIENTIFIC<br>COMPUTING LAB                                 | 0-0-3   | 3     | 2       |

| Т        | ECL 203       | LOGIC DESIGN LAB                                            | 0-0-3   | 3     | 2       |

| R/M      | VAC           | Remedial/Minor course                                       | 3-1-0   | 4**   | 4       |

|          |               | ΤΟΤΑ                                                        | L       | 26/30 | 22/26   |

| A        | PJ A    | BSEMEST                                                 | ER 4     | AL/   | 4M     |

|----------|---------|---------------------------------------------------------|----------|-------|--------|

| TI       |         | INIOI                                                   | $\cap C$ | 110   | 'Λĭ    |

| SLOT     | COURSE  | COURSES                                                 | L-T-P    | HOURS | CREDIT |

|          | NO.     | VIIVEI                                                  | DCI'     | TV    |        |

| Α        | MAT 204 | PROBABILITY,                                            | 3-1-0    | 4     | 4      |

|          |         | RANDOM PROCESS<br>AND NUMERICAL<br>METHODS              |          |       |        |

| В        | ECT202  | ANALOG CIRCUITS                                         | 3-1-0    | 4     | 4      |

| С        | EVT204  | DIGITAL SYSTEM<br>DESIGN                                | 3-1-0    | 4     | 4      |

| D        | ECT 206 | COMPUTER<br>ARCHITECTURE<br>AND<br>MICROCONTROL<br>LERS | 3-1-0    | 4     | 4      |

| E<br>1/2 | EST200  | DESIGN AND<br>ENGINEERING                               | 2-0-0    | 2     | 2      |

|          | HUT200  | PROFESSIONAL<br>ETHICS                                  | 2-0-0    | 2     | 2      |

| F        | MCN202  | CONSTITUTION OF<br>INDIA                                | 2-0-0    | 2     |        |

| S        | ECL 202 | ANALOG CIRCUITS<br>AND SIMULATION<br>LAB                | 0-0-3    | 3     | 2      |

| Т        | ECL 204 | MICROCONTROLLER<br>LAB                                  | 0-0-3    | 3     | 2      |

| R/M/H    | VAC     | Remedial/Minor/Honours                                  | 3-1-0    | 4**   | 4      |

|          |         | TOTAL                                                   | L        | 26/30 | 22/26  |

|          |         | 201                                                     | 4        |       |        |

## **SYLLABUS**

### FOR

# BTECH IN ELECTRONICS (VLSI DESIGN & TECHNOLOGY)

### **THIRD & FOURTH SEMESTERS**

## **SEMESTER - 3**

### ECT201SOLID STATE DEVICESCATEGORYLTPCREDITPCC3104

Preamble: This course aims to understand the physics and working of solid state devices.

Prerequisite: EST130 Basics of Electrical and Electronics Engineering

Course Outcomes: After the completion of the course the student will be able to

| CO1 | Apply Fermi-Dirac Distribution function and Compute carrier concentration at<br>equilibrium and the parameters associated with generation, recombination and |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Transport mechanism                                                                                                                                          |

| CO2 | Explain drift and diffusion currents in extrinsic semiconductors and Compute current density due to these effects.                                           |

| CO3 | Define the current components and derive the current equation in a pn junction diode                                                                         |

|     | And bipolar junction transistor.                                                                                                                             |

| CO4 | Explain the basic MOS physics and derive the expressions for drain current in linear                                                                         |

|     | And saturation regions.                                                                                                                                      |

| CO5 | Discuss scaling of MOSFETs and short channel effects.                                                                                                        |

#### Mapping of course outcomes with program outcomes:

|     | <b>PO 1</b> | <b>PO 2</b> | <b>PO 3</b> | <b>PO 4</b> | PO 5 | <b>PO 6</b> | <b>PO 7</b> | <b>PO 8</b> | <b>PO 9</b> | <b>PO10</b> | PO11 | PO12 |

|-----|-------------|-------------|-------------|-------------|------|-------------|-------------|-------------|-------------|-------------|------|------|

| CO1 | 3           | 3           |             |             |      |             |             |             |             |             |      |      |

| CO2 | 3           | 3           |             |             |      |             |             |             |             |             |      |      |

| CO3 | 3           | 3           |             |             |      |             |             |             |             |             |      |      |

| CO4 | 3           | 3           |             |             |      |             |             |             |             |             |      |      |

| CO5 | 3           |             |             |             |      |             |             |             |             |             |      |      |

#### **Assessment Pattern**

| <b>Bloom's Category</b> | Continuous Assessment Tests |    | <b>End Semester Examination</b> |

|-------------------------|-----------------------------|----|---------------------------------|

|                         | 1                           | 2  |                                 |

| Remember                | 10                          | 10 | 20                              |

| Understand              | 25                          | 25 | 50                              |

| Apply                   | 15                          | 15 | 30                              |

| Analyse                 |                             |    |                                 |

| Evaluate                |                             |    |                                 |

| Create                  |                             |    |                                 |

#### Mark distribution

| Total Marks | CIE | ESE | ESE Duration |

|-------------|-----|-----|--------------|

| 150         | 50  | 100 | 3 hours      |

#### **Continuous Internal Evaluation Pattern:**

| Attendance                             | : 10 marks |

|----------------------------------------|------------|

| Continuous Assessment Test (2 numbers) | : 25 marks |

| Assignment/Quiz/Course project         | : 15 marks |

**End Semester Examination Pattern:** There will be two parts; Part A and Part B. Part A contain 10 questions with 2 questions from each module, having 3 marks for each question. Students should answer all questions. Part B contains 2 questions from each module of which student should answer any one. Each question can have maximum 2 sub-divisions and carry 14 marks.

#### **Course Level Assessment Questions**

Course Outcome 1 (CO1): Compute carrier concentration at equilibrium and the parameters associated with generation, recombination and transport mechanism

- 1. Derive the expression for equilibrium electron and hole concentration.

- 2. Explain the different recombination mechanisms

- 3. Solve numerical problems related to carrier concentrations at equilibrium, energy band diagrams and excess carrier concentrations in semiconductors.

### Course Outcome 2 (CO2) : Compute current density in extrinsic semiconductors in specifiedelectric field and due to concentration gradient.

- 1. Derive the expression for the current density in a semiconductor in response to the applied electric field.

- 2. Derive the expression for diffusion current in semiconductors.

- 3. Show that diffusion length is the average distance a carrier can diffuse before recombining.

### Course Outcome 3 (CO3): Define the current components and derive the current equation in a pn junction diode and bipolar junction transistor.

- 1. Derive ideal diode equation.

- 2. Derive the expression for minority carrier distribution and terminal currents in a BJT.

- 3. Solve numerical problems related to PN junction diode and BJT.

### Course Outcome 4 (CO4): Explain the basic MOS physics with specific reference on MOSFET characteristics and current derivation.

- 1. Illustrate the working of a MOS capacitor in the three different regions of operation.

- 2. Explain the working of MOSFET and derive the expression for drain current.

- 3. Solve numerical problems related to currents and parameters associated with MOSFETs.

### Course Outcome 5 (CO5): Discuss the concepts of scaling and short channel effects of MOSFET.

- 1. Explain the different MOSFET scaling techniques.

- 2. Explain the short channel effects associated with reduction in size of MOSFET.

#### **SYLLABUS**

#### **MODULE I**

Elemental and compound semiconductors, Intrinsic and Extrinsic semiconductors, concept of effective mass, Fermions-Fermi Dirac distribution, Fermi level, Doping & Energy banddiagram, Equilibrium and steady state conditions, Density of states & Effective density of states, Equilibrium concentration of electrons and holes.

Excess carriers in semiconductors: Generation and recombination mechanisms of excess carriers, quasi Fermi levels.

#### **MODULE II**

Carrier transport in semiconductors, drift, conductivity and mobility, variation of mobility with temperature and doping, Hall Effect.

Diffusion, Einstein relations, Poisson equations, Continuity equations, Current flow equations, Diffusion length, Gradient of quasi Fermi level

#### **MODULE III**

PN junctions : Contact potential, Electrical Field, Potential and Charge distribution at the junction, Biasing and Energy band diagrams, Ideal diode equation.

Metal Semiconductor contacts, Electron affinity and work function, Ohmic and Rectifying Contacts, current voltage characteristics.

Bipolar junction transistor, current components, Transistor action, Base width modulation.

#### **MODULE IV**

Ideal MOS capacitor, band diagrams at equilibrium, accumulation, depletion and inversion, threshold voltage, body effect, MOSFET-structure, types, Drain current equation (derive)- linear and saturation region, Drain characteristics, transfer characteristics.

#### **MODULE V**

MOSFET scaling - need for scaling, constant voltage scaling and constant field scaling. Sub

threshold conduction in MOS.

Short channel effects- Channel length modulation, Drain Induced Barrier Lowering, Velocity Saturation, Threshold Voltage Variations and Hot Carrier Effects.

Non-Planar MOSFETs: Fin FET -Structure, operation and advantages

#### **Text Books**

- 1. Ben G. Streetman and Sanjay Kumar Banerjee, Solid State Electronic Devices, Pearson 6/e, 2010 (Modules I, II and III)

- 2. Sung Mo Kang, CMOS Digital Integrated Circuits: Analysis and Design, McGraw-Hill, Third Ed., 2002 (Modules IV and V)

#### **Reference Books**

- 1. Neamen, Semiconductor Physics and Devices, McGraw Hill, 4/e, 2012

- 2. Sze S.M., Semiconductor Devices: Physics and Technology, John Wiley, 3/e, 2005

- 3. Pierret, Semiconductor Devices Fundamentals, Pearson, 2006

- 4. Sze S.M., Physics of Semiconductor Devices, John Wiley, 3/e, 2005

- 5. Achuthan, K N Bhat, Fundamentals of Semiconductor Devices, 1e, McGraw Hill, 2015

- 6. Yannis Tsividis, Operation and Modelling of the MOS Transistor, Oxford University Press.

- 7. Jan M.Rabaey, Anantha Chandrakasan, Borivoje Nikolic, Digital Integrated Circuits A Design Perspective, PHI.

#### Course Contents and Lecture Schedule

| No  | Торіс                                                                  | No. of   |

|-----|------------------------------------------------------------------------|----------|

|     |                                                                        | Lectures |

| 1   | MODULE 1                                                               |          |

| 1.1 | Elemental and compound semiconductors, Intrinsic and Extrinsic         | 2        |

|     | semiconductors, Effective mass                                         |          |

| 1.2 | Fermions-Fermi Dirac distribution, Fermi level, Doping & Energy        | 2        |

|     | band diagram,                                                          |          |

| 1.3 | Equilibrium and steady state conditions, Density of states & Effective | 1        |

|     | density of states                                                      |          |

| 1.4 | Equilibrium concentration of electrons and holes.                      | 1        |

| 1.5 | Excess carriers in semiconductors: Generation and                      | 2        |

|     | recombinationmechanisms of excess carriers, quasi Fermi levels.        |          |

| 2   | MODULE 2                                                               |          |

| 2.1 | Carrier transport in semiconductors, drift, conductivity and           | 2        |

|     | mobility, variation of mobility with temperature and doping.           |          |

| 2.2 | Diffusion equation                                                     | 1        |

| 2.3 | Einstein relations, Poisson equations                                    | 1 |

|-----|--------------------------------------------------------------------------|---|

| 2.4 | Poisson equations, Continuity equations, Current flow equations          | 1 |

| 2.5 | Diffusion length, Gradient of quasi Fermi level                          | 1 |

| 3   | MODULE 3                                                                 |   |

| 3.1 | PN junctions : Contact potential, Electrical Field, Potential and Charge | 2 |

|     | distribution at the junction, Biasing and Energy band diagrams,          |   |

| 3.2 | Ideal diode equation                                                     | 1 |

| 3.3 | Metal Semiconductor contacts, Electron affinity and work function,       | 3 |

|     | Ohmic and Rectifying Contacts, current voltage characteristics.          |   |

| 3.4 | Bipolar junction transistor – working,, current components,              | 2 |

|     | Transistoraction, Base width modulation.                                 |   |

| 3.5 | Derivation of terminal currents in BJT                                   | 2 |

| 4   | MODULE 4                                                                 |   |

| 4.1 | Ideal MOS capacitor, band diagrams at equilibrium, accumulation,         | 2 |

|     | depletion and inversion                                                  |   |

| 4.2 | Threshold voltage, body effect                                           | 1 |

| 4.3 | MOSFET-structure, working, types,                                        | 2 |

| 4.4 | Drain current equation (derive)- linear and saturation region, Drain     | 2 |

|     | characteristics, transfer characteristics.                               |   |

| 5   | MODULE 5                                                                 |   |

| 5.1 | MOSFET scaling – need for scaling, constant voltage scaling and          | 2 |

|     | constant field scaling.                                                  |   |

| 5.2 | Sub threshold conduction in MOS.                                         | 1 |

| 5.3 | Short channel effects- Channel length modulation, Drain Induced          | 3 |

|     | Barrier                                                                  |   |

|     | Lowering, Velocity Saturation, Threshold Voltage Variations and          |   |

|     | Hot CarrierEffects.                                                      |   |

| 5.4 | Non-Planar MOSFETs: Fin FET –Structure, operation and advantages         | 1 |

#### **Model Question paper**

#### **APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY**

#### THIRD SEMESTER B.TECH DEGREE EXAMINATION, **Course Code : ECT201 Course : SOLID STATE DEVICES**

#### **Time: 3 hours**

#### Max. Marks:100

#### PART A

#### Answer *all* questions. Each question carries *3 marks*.

- 1. Draw the energy band diagram of P type and N type semiconductor materials, clearly indicating the different energy levels.

- 2. Indirect recombination is a slow process. Justify

- 3. Explain how mobility of carriers vary with temperature.

- 4. Show that diffusion length is the average length a carrier moves before recombination.

- 5. Derive the expression for contact potential in a PN junction diode.

- 6. Explain Early effect? Mention its effect on terminal currents of a BJT.

- 7. Derive the expression for threshold voltage of a MOSFET.

- 8. Explain the transfer characteristics of a MOSFET in linear and saturation regions.

- 9. Explain Subthreshold conduction in a MOSFET. Write the expression for Subthreshold current.

- 10. Differentiate between constant voltage scaling and constant field scaling

#### PART B

Answer *any one* question from each module. Each question carries 14 marks.

#### **MODULE I**

11. (a) Derive law of mass action

(b) An n-type Si sample with  $N_d = 10^5$  cm<sup>-3</sup> is steadily illuminated such that  $g_{op}=10^{21}$ EHP/cm<sup>3</sup> s. If  $\tau_n = \tau_p = 1 \mu s$  for this excitation. Calculate the separation in the Quasi- Fermi levels  $(F_n-F_p)$ . Draw the Energy band diagram . (6 marks)

12. (a) Draw and explain Fermi Dirac Distribution function and position of Fermi level in intrinsic and extrinsic semiconductors. (8 marks)

(b)The Fermi level in a Silicon sample at 300 K is located at 0.3 eV below the bottom of the conduction band. The effective densities of states  $N_C = 3.22 \times 10^{19} \text{ cm}^{-3}$  and  $N_V = 1.83 \times 10^{19} \text{ cm}^{-3}$  $10^{19}$  cm<sup>-3</sup>. Determine

(a) the electron and hole concentrations at 300K.

(b) the intrinsic carrier concentration at 400 K.

(8 marks)

(6 marks)

#### **MODULE II**

- 13. (a) Derive the expression for mobility, conductivity and Drift current density in a semiconductor. (8 marks)

(b) A Si bar 0.1 μm long and 100 μm<sup>2</sup> in cross-sectional area is doped with 10<sup>17</sup> cm<sup>-3</sup> phosphorus. Find the current at 300 K with 10 V applied. How long will it take an average electron to drift 1 μm in pure Si at an electric field of 100 V/cm? (6 marks)

- 14. (a) A GaAs sample is doped so that the electron and hole drift current densities are equal in an applied electric field. Calculate the equilibrium concentration of electron and hole, the net doping and the sample resistivity at 300 K. Given  $\mu_n = 8500 \text{ cm}^2/\text{Vs}$ ,  $\mu_p = 400 \text{ cm}^2/\text{Vs}$ ,  $n_i = 1.79 \text{ x } 10^6 \text{ cm}^{-3}$ . (7 marks)

(b) Derive the steady-state diffusion equations in semiconductor. (6 marks)

#### **MODULE III**

- 15. (a) Derive the expression for ideal diode equation. State the assumptions use (9 marks) (b) Boron is implanted into an n-type Si sample ( $N_d = 10^{16} \text{cm}^{-3}$ ), forming an abrupt junction of square cross section with area = 2 x 10<sup>-3</sup> cm<sup>2</sup>. Assume that the acceptor concentration in the p-type region is  $N_a = 4 \times 10^{18} \text{ cm}^{-3}$ . Calculate  $V_0$ , W, Q+, and E<sub>0</sub> for this junction at equilibrium (300 K). (5 marks)

- 16. With the aid of energy band diagrams, explain how a metal N type Schottky contact function as rectifying and ohmic contacts. (14 marks)

#### **MODULE IV**

- 17. (a) Starting from the fundamentals, derive the expression for drain current of a MOSFET in the two regions of operation. (8 Marks)

(b) Find the maximum depletion width, minimum capacitance C<sub>i</sub>, and threshold voltagefor an ideal MOS capacitor with a 10-nm gate oxide (Si0<sub>2</sub>) on p-type Si with N<sub>a</sub> = 10<sup>16</sup> cm<sup>-3</sup>. Include the effects of flat band voltage, assuming an n + polysilicon gate and fixed oxide charge of 5 x 10<sup>10</sup> q (C/cm<sup>2</sup>). (6 marks)

- 18. (a) Explain the CV characteristics of an ideal MOS capacitor (8 Marks)

(b) For a long channel n-MOSFET with W = 1V, calculate the V<sub>G</sub> required for an I<sub>D(sat.)</sub> of

0.1 mA and V<sub>D(sat.)</sub> of 5V. Calculate the small-signal output conductance g and V the transconductance g m(sat.) at V<sub>D</sub> = 10V. Recalculate the new I<sub>D</sub> for (V<sub>G</sub> V<sub>T</sub>) = 3 and V<sub>D</sub> = 4V. (6 marks)

#### **MODULE V**

- 19. Explain Drain induced barrier lowering, Velocity Saturation, Threshold Voltage Variations and Hot Carrier Effects associated with scaling down of MOSFETs. (14 marks)

- 20. With the aid of suitable diagrams explain the structure and working of a FINFET. List its advantages. (14 marks)

| ECT203 | LOGIC CIRCUIT DESIGN | CATEGORY | L | Т | P | CREDIT |

|--------|----------------------|----------|---|---|---|--------|

|        |                      | PCC      | 3 | 1 | 0 | 4      |

**Preamble:** This course aims to impart the basic knowledge of logic circuits and enablestudents to apply it to design a digital system.

Prerequisite: EST130 Basics of Electrical and Electronics Engineering

Course Outcomes: After the completion of the course the student will be able to

| CO1 | Explain the elements of digital system abstractions such as digital representations of information, digital logic and Boolean algebra |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| CO2 | Create an implementation of a combinational logic function described by a truth table using and/or/inv gates/ muxes                   |

| CO3 | Compare different types of logic families with respect to performance and efficiency                                                  |

| CO4 | Design a sequential logic circuit using the basic building blocks like flip-flops                                                     |

| CO5 | Design and analyze combinational and sequential logic circuits through gate level Verilog models.                                     |

#### Mapping of course outcomes with program outcomes

|     | <b>PO 1</b> | <b>PO 2</b> | <b>PO 3</b> | <b>PO 4</b> | <b>PO 5</b> | <b>PO 6</b> | <b>PO 7</b> | <b>PO 8</b> | PO 9 | PO10 | PO11 | PO12 |

|-----|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------|------|------|------|

| CO1 | 3           | 3           |             |             |             |             |             |             |      |      |      |      |

| CO2 | 3           | 3           | 3           |             |             |             |             |             |      |      |      |      |

| CO3 | 3           | 3           |             |             |             |             |             |             |      |      |      |      |

| CO4 | 3           | 3           | 3           |             |             |             |             |             |      |      |      |      |

| CO5 | 3           | 3           | 3           |             |             |             |             |             |      |      |      |      |

#### **Assessment Pattern**

| <b>Bloom's Category</b> | Continuous As | ssessment Tests | End Semester Examination |  |  |  |

|-------------------------|---------------|-----------------|--------------------------|--|--|--|

|                         | 1             | 2               |                          |  |  |  |

| Remember                | 10            | 10              | 20                       |  |  |  |

| Understand              | 25            | 25              | 50                       |  |  |  |

| Apply                   | 15            | 15              | 30                       |  |  |  |

| Analyse                 |               |                 |                          |  |  |  |

| Evaluate                |               |                 |                          |  |  |  |

| Create                  |               |                 |                          |  |  |  |

#### Mark distribution

| Total Marks | CIE | ESE | ESE Duration |

|-------------|-----|-----|--------------|

| 150         | 50  | 100 | 3 hours      |

#### **Continuous Internal Evaluation Pattern:**

Attendance

: 10 marks

| Continuous Assessment Test (2 numbers) | : 25 marks |

|----------------------------------------|------------|

| Course project                         | : 15 marks |

It is mandatory that a *course project* shall be undertaken by a student for this subject. The course project can be performed either as a hardware realization/simulation of a typical digital system using combinational or sequential logic. Instead of two assignments, two evaluations may be performed on the course project along with series tests, each carrying 5 marks. Upon successful completion of the project, a brief report shall be submitted by the student which shall be evaluated for 5 marks. The report has to be submitted for academic auditing. A few samples projects are given below:

#### Sample course projects:

1. M-Sequence Generator Psuedo random sequences are popularly used in wireless communication. A sequence generator is used to produce pseudo random codes that are useful in spread spectrum applications. Their generation relies on irreducible polynomials. A maximallength sequence generator that relies on the polynomial  $P(D) = D^7 + D^3 + 1$ , with each D represent delay of one clock cycle.

- An 8-bit shift register that is configured as a ring counter may be used realize the above equation.

- This circuit can be developed in verilog, simulated, synthesized and programmed into a tinyFPGA and tested in real time.

- Observe the M-sequnce from parallel outputs of shift register for one period . Count thenumber of 1s and zeros in one cycle.

- Count the number of runs of 1s in singles, pairs, quads etc. in the pattern.

#### 2. BCD Subtractor

- Make 4 -bit parallel adder circuit in verilog.

- Make a one digit BCD subtracter in Verilog, synthesize and write into a tiny FPGA.

- Test the circuit with BCD inputs.

#### 3. Digital Thermometer

- Develop a circuit with a temperature sensor and discrete components to measure and dispaly temperature.

- Solder the circuit on PCB and test it.

#### 4. Electronic Display

- This display should receive the input from an alphanumeric keyboard and display it on an LCD diplay.

- The decoder and digital circuitry is to developed in Verilog and programmed into a tiny FPGA.

#### 5. Electronic Roulette Wheel

- 32 LEDs are placed in a circle and numbered that resembles a roulette wheel.

- A 32-bit shift register generates a random bit pattern with a single 1 in it.

- When a push button is pressed the single 1 lights one LED randomly.

- Develop the shift register random pattern generator in verilog and implement on a tiny FPGA and test the circuit.

- 6. Three Bit Carry Look Ahead Adder

- Design the circuit of a three bit carry look ahead adder.

- Develop the verilog code for it and implement and test it on a tiny FPGA. Compare the performance with a parallel adder.

**End Semester Examination Pattern:** There will be two parts; Part A and Part B. Part A contain 10 questions with 2 questions from each module, having 3 marks for each question. Students should answer all questions. Part B contains 2 questions from each module of which student should answer any one. Each question can have maximum 2 sub-divisions and carry 14 marks. The questions on verlog modelling should not have a credit more than 25% of the whole mark

#### **Course Level Assessment Questions**

#### Course Outcome 1 (CO1) : Number Systems and Codes

- 1. Consider the signed binary numbers A = 01000110 and B = 11010011 where B is in 2's complement form. Find the value of the following mathematical expression (i) A + B(ii)A B

- 2. Perform the following operations (i)D9CE<sub>16</sub>-CFDA<sub>16</sub> (ii) 6575<sub>8</sub>-5732<sub>8</sub>

- 3. Convert decimal 6,514 to both BCD and ASCII codes. For ASCII, an even parity bit is tobe appended at the left.

#### Course Outcome 2 (CO2) : Boolean Postulates and combinational circuits

- 1. Design a magnitude comparator to compare two 2-bit numbers  $A = A_1A_0$  and  $B = B_1B_0B_2$ . Simplify using K-map F(a,b,c,d) =  $\Sigma$  m (4,5,7,8,9,11,12,13,15)

- 2. Explain the operation of a 8x1 multiplexer and implement the following using an 8x1 multiplexer  $F(A, B, C, D) = \Sigma m (0, 1, 3, 5, 6, 7, 8, 9, 11, 13, 14)$

#### Course Outcome 3 (CO3) : Logic families and its characteristics

- 1. Define the terms noise margin, propagation delay and power dissipation of logic families. Compare TTL and CMOS logic families showing the values of above mentioned terms.

- 2. Draw the circuit and explain the operation of a TTL NAND gate

- 3. Compare TTL, CMOS logic families in terms of fan-in, fan-out and supply voltage

#### Course Outcome 4 (CO4) : Sequential Logic Circuits

- 1. Realize a T flip-flop using NAND gates and explain the operation with truth table, excitation table and characteristic equation

- 2. Explain a MOD 6 asynchronous counter using JK Flip Flop

- 3. Draw the logic diagram of 3 bit PIPO shift register with LOAD/SHIFT control and explain its working

#### Course Outcome 5 (CO5) : Logic Circuit Design using HDL

- 1. Design a 4-to-1 mux using gate level Verilog model.

- 2. Design a verilog model for a hald adder circuit. Make a one bit full adder by connectingtwo half adder models.

- 3. Compare concurrent signal assignment versus sequential signal assignment.

#### **Syllabus**

#### Module 1: Number Systems and Codes:

Binary and hexadecimal number systems; Methods of base conversions; Binary and hexadecimal arithmetic; Representation of signed numbers; Fixed and floating point numbers; Binary coded decimal codes; Gray codes; Excess 3 code. Alphanumeric codes: ASCII. Basics of verilog -- basic language elements: identifiers, data objects, scalar data types, operators.

#### **Module 2: Boolean Postulates and Fundamental Gates**

Boolean postulates and laws – Logic Functions and Gates De-Morgan's Theorems, Principle of Duality, Minimization of Boolean expressions, Sum of Products (SOP), Product of Sums (POS), Canonical forms, Karnaugh map Minimization. Modeling in verilog, Implementation of gates with simple verilog codes.

#### Module 3: Combinatorial and Arithmetic Circuits

Combinatorial Logic Systems - Comparators, Multiplexers, Demultiplexers, Encoder, Decoder. Half and Full Adders, Subtractors, Serial and Parallel Adders, BCD Adder. Modeling and simulation of combinatorial circuits with verilog codes at the gate level.

#### Module 4: Sequential Logic Circuits:

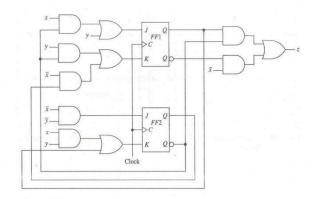

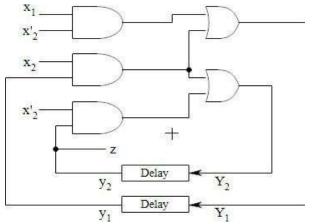

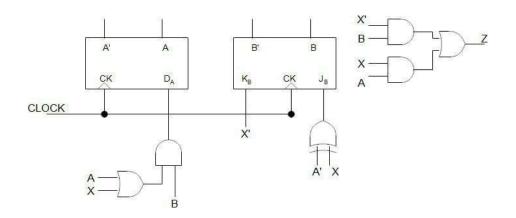

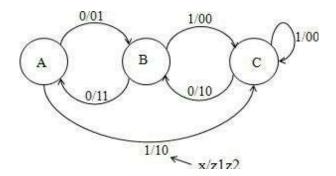

Building blocks like S-R, JK and Master-Slave JK FF, Edge triggered FF, Conversion of Flipflops, Excitation table and characteristic equation. Implementation with verilog codes. Ripple and Synchronous counters and implementation in verilog, Shift registers-SIPO, SISO, PISO, PIPO. Shift Registers with parallel Load/Shift, Ring counter and Johnsons counter. Asynchronous and Synchronous counter design, Mod N counter. Modeling and simulation of flipflops and counters in verilog.

#### odule 5: Logic families and its characteristics:

TTL, ECL, CMOS - Electrical characteristics of logic gates – logic levels and noise margins, fanout, propagation delay, transition time, power consumption and power-delay product. TTL inverter - circuit description and operation; CMOS inverter - circuit description and operation; Structure and operations of TTL and CMOS gates; NAND in TTL and CMOS, NAND and NOR in CMOS.

#### **Text Books:**

- 1. Mano M.M, Ciletti M.D., -Digital Designl, Pearson India, 4th Edition. 2006

- 2. D.V. Hall, -Digital Circuits and Systems<sup>II</sup>, Tata McGraw Hill, 1989

- 3. S. Brown, Z. Vranesic, -Fundamentals of Digital Logic with Verilog Design<sup>I</sup>, McGraw Hill.

- 4. Samir Palnika r—Verilog HDL: A Guide to Digital Design and Syntheisl, SunsoftPress.

- 5. R.P. Jain, -Modern digital Electronics<sup>II</sup>, Tata McGraw Hill, 4th edition, 2009

#### **Reference Books:**

- 1. W.H. Gothmann, -Digital Electronics An introduction to theory and practicell, PHI,2<sup>nd</sup> edition ,2006

- 2. Wakerly J.F., -Digital Design: Principles and Practices, Pearson India, 4th 2008

- 3. A. Ananthakumar , "Fundamentals of Digital Circuits", Prentice Hall, 2nd edition, 2016

- 4. Fletcher, William I., An Engineering Approach to Digital Design, 1st Edition, Prentice Hall India, 1980

#### **Course Contents and Lecture Schedule**

| No  | Торіс                                                                   | No. of   |

|-----|-------------------------------------------------------------------------|----------|

|     |                                                                         | Lectures |

| 1   | Number Systems and Codes:                                               |          |

| 1.1 | Binary, octal and hexadecimal number systems; Methods of base           | 2        |

|     | conversions;                                                            |          |

| 1.2 | Binary, octal and hexadecimal arithmetic;                               | 1        |

| 1.3 | Representation of signed numbers; Fixed and floating point numbers;     | 3        |

| 1.4 | Binary coded decimal codes; Gray codes; Excess 3 code :                 | 1        |

| 1.5 | Error detection and correction codes - parity check codes and           | 3        |

|     | Hamming code-Alphanumeric codes:ASCII                                   |          |

| 1.6 | Verilog basic language elements: identifiers, data objects, scalar data | 2        |

|     | types,operators                                                         |          |

| 2   | <b>Boolean Postulates and Fundamental Gates:</b>                        |          |

| 2.1 | Boolean postulates and laws – Logic Functions and Gates, De-            | 2        |

|     | Morgan's Theorems, Principle of Duality                                 |          |

| 2.2 | Minimization of Boolean expressions, Sum of Products (SOP), Product     | 2        |

|     | of Sums (POS)                                                           |          |

| 2.3 | Canonical forms, Karnaugh map Minimization                              | 1        |

| 2.4 | Gate level modelling in Verilog: Basic gates, XOR using NAND and        | 2        |

|     | NOR                                                                     |          |

| 3   | Combinatorial and Arithmetic Circuits                                   |          |

| 3.1 | Combinatorial Logic Systems - Comparators, Multiplexers,                | 2        |

|     | Demultiplexers                                                         |   |

|-----|------------------------------------------------------------------------|---|

| 3.2 | Encoder, Decoder, Half and Full Adders, Subtractors, Serial and        | 3 |

|     | ParallelAdders, BCD Adder                                              |   |

| 3.3 | Gate level modelling combinational logic circuits in Verilog: half     | 3 |

|     | adder, full adder, mux, demux, decoder, encoder                        |   |

| 4   | Sequential Logic Circuits:                                             |   |

| 4.1 | Building blocks like S-R, JK and Master-Slave JK FF, Edge triggered FF | 2 |

| 4.2 | Conversion of Flipflops, Excitation table and characteristic equation. | 1 |

| 4.3 | Ripple and Synchronous counters, Shift registers-                      | 2 |

|     | SIPO.SISO,PISO,PIPO                                                    |   |

| 4.4 | Ring counter and Johnsons counter, Asynchronous and Synchronous        | 3 |

|     | counter design                                                         |   |

| 4.5 | Mod N counter, Random Sequence generator                               | 1 |

| 4.6 | Modelling sequential logic circuits in Verilog: flipflops, counters    | 2 |

| 5   | Logic families and its characteristics:                                |   |

| 5.1 | TTL,ECL,CMOS- Electrical characteristics of logic gates – logic levels | 3 |

|     | andnoise margins, fan-out, propagation delay, transition time, power   |   |

|     | consumption and power-delay product.                                   |   |

| 5.2 | TTL inverter - circuit description and operation                       | 1 |

| 5.3 | CMOS inverter - circuit description and operation                      | 1 |

| 5.4 | Structure and operations of TTL and CMOS gates; NAND in TTL,           | 2 |

|     | NAND and NOR in CMOS.                                                  |   |

#### Simulation Assignments (ECT203)

The following simulations can be done in QUCS, KiCad or PSPICE.

#### **BCD Adder**

- Realize a one bit paraller adder, simulate and test it.

- Cascade four such adders to form a four bit parallel adder.

- Simulate it and make it into a subcircuit.

- Develop a one digit BCD adder, based on the subcircuit, simulate and test it

#### **BCD Subtractor**

- Use the above 4 -bit adder subcircuit, implement and simulate a one digit BCD subtractor.

- Test it with two BCD inputs

#### Logic Implementation with Multiplexer

- Develop an 8 : 1 multiplexer using gates, simulate, test and make it into a subcircuit.

- Use this subcircuit to implement the logic function  $f(A, B, C) = \Sigma m(1, 3, 7)$ Modify the truth table properly and implement the logic function  $f(A, B, C, D) = \Sigma m(1, 4, 12, 14)$ using one 8 : 1 multiplexer.

#### **BCD to Seven Segment Decoder**

- Develop a BCD to seven segment decoder using gates and make it into a sub circuit.

- Simulate this and test it.

#### **Ripple Counters**

• Understand the internal circuit of 7490 IC and develop it in the simulator.

Make it into a subcircuit and simulate it. Observe the truth table and timing diagrams formod-5, mod-2 and mod-10 operation.

- Develop a mod-40 (mod-8 and mod-5) counter by cascading two such subcircuits.

- Simulate and observe the timing diagram and truth table.

#### **Synchronous Counters**

- Design and develop a 4-bit synchronous counter using J-K flip-flops.

- Perform digital simulation and observe the timing diagram and truth table.

#### **Sequence Generator**

• Connect D flip-flops to realize and 8-bit shift register and make it into a sub circuit.

Sequence generator that relies on the polynomial  $P(D) = D_7 + D_3 + 1$ , with each D represented y of one clock cycle

• Simulate and observe this maximal length pseudo random sequence.

#### **Transfer Characteristics of TTL and CMOS Inverters**

Develop a standard TTL circuit and perform sweep simulation and observe the transfer characteristics. Compute the threshold voltage and noise margins.

Develop and simulate standard CMOS inverter circuit and perform sweep simulation and observe the transfer characteristics. Compute the threshold voltage and noise margins.

#### **Model Question paper**

#### APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

#### THIRD SEMESTER B.TECH DEGREE EXAMINATION, Course Code:ECT203 Course : Logic Circuit Design

Time: 3 hours

Max. Marks:100

#### PART A

#### Answer *all* questions. Each question carries *3 marks*.

- 1. Convert  $203.52_{10}$  to binary and hexadecimal.

- 2. Compare bitwise and logical verilog operators.

- 3. Prove that NAND and NOR are not associative.

- 4. Convert the expression ABCD+ABC+ACD to minterms.

- 5. Define expressions in Verilog with example.

- 6. Explain the working of a decoder.

- 7. What is race around condition?

- 8. Convert a T flip-flop to D flip-flop.

- 9. Define fan-in and fan-out of logic circuits.

- 10. Define noise margin and how can you calculate it?

#### PART B

Answer *any one* question from each module. Each question carries 14 marks.

#### **MODULE I**

11. a. Subtract 4610 from 10010 using 2's complement arithmetic.(8 marks) b.Give a brief description on keywords and identifiers in Verilog with example.(6 marks)

| 12. | a. Explain the floating and fixed point representation of numbers. | (8 marks) |

|-----|--------------------------------------------------------------------|-----------|

|     | b. Explain the differences between programming lanuguages and HDLs | (6 marks) |

#### **MODULE II**

13. a. Simplify  $f(A, B, C, D) = \sum m(4, 5, 7, 8, 9, 11, 12, 13, 15)$  using K-maps.(7 marks)b. Write a Verilog code for implementing above function(7 marks)

## 14. a. Write a Verilog code to implement the basic gates. (7 marks) b. Reduce the following Boolean function using K-Map and implement the simplified function using the logic gates f (A, B, C, D) = ∑(0, 1, 4, 5, 6, 8, 9, 10, 12, 13, 14) (7 marks)

#### Module III

| 15. a. Design a 3-bit magnitude comparator circuit.                                         | (8 marks)         |

|---------------------------------------------------------------------------------------------|-------------------|

| b. Write a Verilog description for a one bit full adder circuit.                            | (6 marks)         |

| 16. a. Write a verilog code to implement 4:1 multiplexer                                    | (6 marks) b.      |

| Implement the logic function f (A, B, C) = $\sum m(0, 1, 4, 7)$ using 8 : 1 and 4 (8 marks) | : 1 multiplexers. |

| Module IV                                                                                   |                   |

| 17. Design MOD 12 asynchronous counter using T flip-flop.                                   | (14 marks)        |

| 18. a. Explain the operation of Master Slave JK flipflop.                                   | (7 marks)         |

| b. Derive the ouput Qn+1 in Terms of Jn, Kn and Qn.                                         | (7 marks)         |

#### Module V

| 19. | <ul><li>a. Explain in detail about TTL with open collector output configuration.</li><li>b. Draw an ECL basic gate and explain.</li></ul> | (8 marks)<br>(6 marks) |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 20. | a. Demonstrate the CMOS logic circuit configuration and characteristics in det                                                            | ail.                   |

(8 marks) b. Compare the characteristics features of TTL and ECL digital logic families. (6 marks)

| ECT205 | NETWORK THEORY | CATEGORY | L | Т | P | CREDIT |

|--------|----------------|----------|---|---|---|--------|

|        |                | PCC      | 3 | 1 | 0 | 4      |

**Preamble:** This course aims to analyze the linear time invariant electronic circuits.

Prerequisite: EST130 Basics of Electrical and Electronics Engineering

Course Outcomes: After the completion of the course the student will be able to

| CO1 | Apply Mesh / Node analysis to obtain steady state response of the linear time invariant networks. |

|-----|---------------------------------------------------------------------------------------------------|

| CO2 | Apply Network Theorems to obtain steady state response of the linear time invariant networks.     |

| CO3 | Apply Laplace Transforms to determine the transient behavior of RLC networks.                     |

| CO4 | Apply Network functions to analyze the single port and twoport networks.                          |

| CO5 | Apply Network Parameters to analyze the single port and two port networks.                        |

#### Mapping of course outcomes with program outcomes

|            | <b>PO 1</b> | <b>PO 2</b> | PO 3 | <b>PO 4</b> | <b>PO 5</b> | PO 6 | <b>PO 7</b> | PO 8 | PO 9 | PO10 | PO11 | PO12 |

|------------|-------------|-------------|------|-------------|-------------|------|-------------|------|------|------|------|------|

| CO1        | 3           | 3           | 2    |             |             |      |             |      |      | 2    |      | 2    |

| CO2        | 3           | 3           | 2    |             |             |      |             |      |      | 2    |      | 2    |

| CO3        | 3           | 3           | 2    |             |             |      |             |      |      | 2    |      | 2    |

| <b>CO4</b> | 3           | 3           | 2    |             |             |      |             |      |      | 2    |      | 2    |

| CO5        | 3           | 3           | 2    |             |             |      |             |      |      | 2    |      | 2    |

#### Assessment Pattern

| <b>Bloom's Category</b> | Continuous As | sessment Tests | <b>End Semester Examination</b> |  |  |

|-------------------------|---------------|----------------|---------------------------------|--|--|

|                         | 1             | 2              |                                 |  |  |

| Remember                | 10            | 10             | 10                              |  |  |

| Understand              | 20            | 20             | 20                              |  |  |

| Apply                   | 20            | 20             | 70                              |  |  |

| Analyse                 |               |                |                                 |  |  |

| Evaluate                |               |                |                                 |  |  |

| Create                  |               |                |                                 |  |  |

#### Mark distribution

| Total Marks | CIE | ESE | ESE Duration |

|-------------|-----|-----|--------------|

| 150         | 50  | 100 | 3 hours      |

#### **Continuous Internal Evaluation Pattern:**

| Attendance                             | : 10 marks |

|----------------------------------------|------------|

| Continuous Assessment Test (2 numbers) | : 25 marks |

| Assignment/Quiz/Course project         | : 15 marks |

**End Semester Examination Pattern:** There will be two parts; Part A and Part B. Part A contain 10 questions with 2 questions from each module, having 3 marks for each question. Students should answer all questions. Part B contains 2 questions from each module of which student should answer any one. Each question can have maximum 2 sub-divisions and carry 14 marks.

#### **Course Level Assessment Questions**

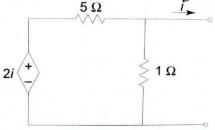

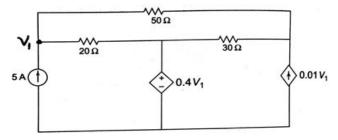

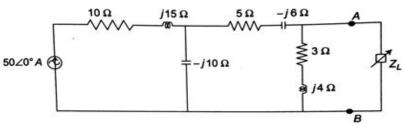

### Course Outcome 1 (CO1): Obtain steady state response of the network using Mesh / node analysis.

- 1. Enumerate different types of sources in electronic networks.

- 2. Solve networks containing independent and dependent sources using Mesh / Node analysis.

- 3. Evolve the steady-state AC analysis of a given network using Mesh or Node analysis.

### Course Outcome 2 (CO2) : Obtain steady state response of the network using Network Theorems.

- 1. Determine the branch current of the given network with dependent source using superposition theorem.

- 2. State and prove Maximum Power Transfer theorem.

- 3. Find the Thevenin's / Norton's equivalent circuit across the port of a given network having dependent source.

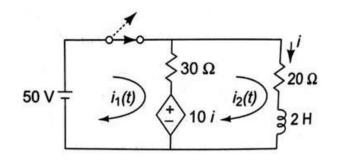

### Course Outcome 3 (CO3): Determine the transient behaviour of network using Laplace Transforms

- 1. The switch is opened at t = 0 after steady state is achieved in given network. Find the expression for the transient output current.

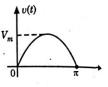

- 2. Find the Laplace Transform of a given waveform.

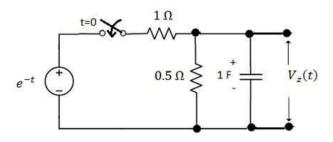

- 3. In the given circuit, the switch is closed at t = 0, connecting an energy source to the R,C,L circuit. At time t = 0, it is observed that capacitor voltage has an initial value. For the element values given, determine expression for output voltage after converting the circuit into transformed domain.

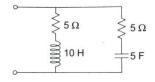

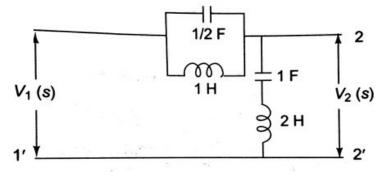

### Course Outcome 4 (CO4): Apply Network functions to analyze the single port and twoport network.

1. What are the necessary conditions for a network driving point function and Transfer functions?

- 2. Evaluate the Driving point function and Transfer function for the given network,

- 3. Plot the poles and zeros of the given network.

#### **Course Outcome 5 (C35): Apply Network Parameters to analyze the two port network.**

- 1. Deduce the transmission parameters of two port network in terms of two port network parameters.

- 2. Define the condition for a two port network to be reciprocal.

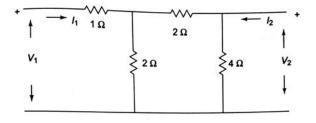

- 3. Two identical sections of the given networks are connected in parallel. Obtain the two port network parameters of the combination.

#### SYLLABUS

#### Module 1 : Mesh and Node Analysis

Mesh and node analysis of network containing independent and dependent sources. Supermesh and Supernode analysis. Steady-state AC analysis using Mesh and Node analysis.

#### Module 2 : Network Theorems

Thevenin's theorem, Norton's theorem, Superposition theorem, Reciprocity theorem, Maximum power transfer theorem. (applied to both dc and ac circuits having dependent source).

#### Module 3 : Application of Laplace Transforms

Review of Laplace Transforms and Inverse Laplace Transforms, Initial value theorem & Final value theorem, Transformation of basic signals and circuits into s-domain.

Transient analysis of RL, RC, and RLC networks with impulse, step and sinusoidal inputs (with and without initial conditions). Analysis of networks with transformed impedance anddependent sources.

#### Module 4 : Network functions

Network functions for the single port and two port network. Properties of driving point and transfer functions. Significance of Poles and Zeros of network functions, Time domainresponse from pole zero plot. Impulse Function & Response. Network functions in the sinusoidal steady state, Magnitude and Phase response.

#### Module 5 : Two port network Parameters

Impedance, Admittance, Transmission and Hybrid parameters of two port network. Interrelationship among parameter sets. Series and parallel connections of two port networks. Reciprocal and Symmetrical two port network. Characteristic impedance, Image impedance and propagation constant (derivation not required)

#### **Text Books**

- 1. Valkenburg V., -Network Analysisl, Pearson, 3/e, 2019.

- 2. Sudhakar A, Shyammohan S. P., -Circuits and Networks- Analysis and Synthesis<sup>II</sup>, McGraw Hill,5/e, 2015.

#### **Reference Books**

- 1. Edminister, -Electric Circuits Schaum's Outline Series , McGraw-Hill, 2009.

- 2. W. Hayt, J. Kemmerly, J. Phillips, S. Durbin, -Engineering Circuit Analysis, McGraw Hill.

- 3. K. S. Suresh Kumar, -Electric Circuits and Networksl, Pearson, 2008.

- 4. William D. Stanley, –Network Analysis with Applications ||, 4/e, Pearson, 2006.

- 5. Ravish R., -Network Analysis and Synthesis ||, 2/e, McGraw-Hill, 2015.

#### **Course Contents and Lecture Schedule**

| No  | Торіс                                                                     | No. of   |

|-----|---------------------------------------------------------------------------|----------|

|     |                                                                           | Lectures |

| 1   | Mesh and Node Analysis                                                    |          |

| 1.1 | Review of circuit elements and Kirchhoff's Laws                           | 2        |

| 1.2 | Independent and dependent Sources, Source transformations                 | 1        |

| 1.3 | Mesh and node analysis of network containing independent and dependent    | 3        |

|     | sources                                                                   |          |

| 1.4 | Supermesh and Supernode analysis                                          | 1        |

| 1.5 | Steady-state AC analysis using Mesh and Node analysis                     | 3        |

| 2   | Network Theorems (applied to both dc and ac circuits having dependent     |          |

|     | source)                                                                   |          |

| 2.1 | Thevenin's theorem                                                        | 1        |

| 2.2 | Norton's theorem                                                          | 1        |

| 2.3 | Superposition theorem                                                     | 2        |

| 2.4 | Reciprocity theorem                                                       | 1        |

| 2.5 | Maximum power transfer theorem                                            | 2        |

| 3   | Application of Laplace Transforms                                         |          |

| 3.1 | Review of Laplace Transforms                                              | 2        |

| 3.2 | Initial value theorem & Final value theorem (Proof not necessary)         | 1        |

| 3.3 | Transformation of basic signals and circuits into s-domain                | 2        |

| 3.4 | Transient analysis of RL, RC, and RLC networks with impulse, step, pulse, | 3        |

|     | exponential and sinusoidal inputs                                         |          |

| 3.5 | Analysis of networks with transformed impedance and dependent sources     | 3        |

| 4   | Network functions                                                         |          |

| 4.1 | Network functions for the single port and two port network                | 2        |

| 4.2 | Properties of driving point and transfer functions                        | 1        |

| 4.3 | Significance of Poles and Zeros of network functions, Time domain     | 1 |

|-----|-----------------------------------------------------------------------|---|

|     | response from pole zero plot                                          |   |

| 4.4 | Impulse Function & Response                                           | 1 |

| 4.5 | Network functions in the sinusoidal steady state, Magnitude and Phase | 3 |

|     | response                                                              |   |

| 5   | Two port network Parameters                                           |   |

| 5.1 | Impedance, Admittance, Transmission and Hybrid parameters of two port | 4 |

|     | network                                                               |   |

| 5.2 | Interrelationship among parameter sets                                | 1 |

| 5.3 | Series and parallel connections of two port networks                  | 2 |

| 5.4 | Reciprocal and Symmetrical two port network                           | 1 |

| 5.5 | Characteristic impedance, Image impedance and propagation constant    | 1 |

|     | (derivation not required)                                             |   |

#### Simulation Assignments:

At least one assignment should be simulation of steady state and transient analysis of R, L, C circuits with different types of energy sources on any circuit simulation software. Samples of simulation assignments are listed below. The following simulations can be done in QUCS, KiCad or PSPICE.

1. Make an analytical solution of Problem 4.3 in page 113 of the book *Network Analysis* by M EVan Valkenberg. Realize this circuit in the simulator and observe i(t) and  $V_2(t)$  using transient simulation.

- 2. Realize a series RLC circuit with

- $R = 200\Omega, L = 0.1H, C = 13.33\mu F$

- $R = 200\Omega$ , L = 0.1H,  $C = 10\mu F$  and

•  $R = 200\Omega$ , L = 0.1H,  $C = 1\mu F$  and no source respectively. The initial voltage across the capacitor is 200V Simulate the three circuits, and observe the current *i(t)* through them.

3. Repeat the above assignment for the three set of component values for a parallel RLC circuit.

4. Refer Problem 9.18 in page 208 in the book *Electric Circuits* by Nahvi and Edminister 4<sup>th</sup> Edition. See Fig. 9.28. Simulate this circuit to verify superposition theorem for the three current with individual sources and combination.

5. Refer Problem 9.22 in page 210 in the book *Electric Circuits* by Nahvi and Edminister 4<sup>th</sup> Edition. See Fig. 9.32. Implement the circuit on the simulator with  $V = 30 < 30^{\circ}$ . Verify the duality between the sources V and the current *I2* and *I3* using simulation.

6. See Fig. 12.40 in Chapter 12 (page 298) in the above book. Let  $R1 = R2 = 2k\Omega$ , L = 10mH and C = 40nF. Implement this circuit in the simulator and perform the ac analysisto plot the frequency response.

#### **Model Question paper**

#### APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY

THIRD SEMESTER B.TECH DEGREE EXAMINATION,

#### **Course Code:ECT205**

#### **Course: NETWORK THEORY**

Time: 3 hours

Max. Marks:100

#### PART A

Answer *all* questions. Each question carries *3 marks*.

- 1. Illustrate the source-transformation techniques.

- 2. Explain the concept of super node.

- 3. State and prove Maximum Power Transfer theorem

- 4. Evaluate the Norton's equivalent current in the following circuit.

5. Evaluate the Laplace Transform of half-wave rectified sine pulse

- 6. Give the two forms of transformed impedance equivalent circuit of a capacitor with initial charge across it.

- 7 Enumerate necessary condition for a Network Functions to be Transfer Functions.

- 8 Obtain the pole zero configuration of the impedance function of the followingcircuit.

- 9 Define the short-circuit admittance parameter with its equivalent circuit.

- 10 Deduce Z-parameter in terms of h-parameter.

#### PART B

Answer any one question from each module. Each question carries 14 marks.

#### **MODULE I**

11 a. Find the voltage  $V_1$  using nodal analysis.

(7 marks)

b. Find the current through 8 ohms resistor in the following circuit using mesh analysis.

(7 marks)

12 a. Find the power delivered by the 5A current source using nodal analysis method. (7 marks)

b. Determine the values of source currents using Mesh analysis (7marks)

b. Find the Norton's equivalent circuit across the port AB.

14 Determine the maximum power delivered to the load in the circuit. (14 marks)

#### **MODULE III**

15 a. The switch is opened at t = 0 after steady state is achieved. Find the expression for the transient current i.(8 marks)

(7marks)

b. A voltage pulse of unit height and width \_ T ' is applied to a low pass RC circuit at time t=0.Determine the expression for the voltage across the capacitor C as a function of time. (6 marks)

16 In the circuit, the switch is closed at t = 0, connecting a source  $e^{-t}$  to the RC circuit. At time, t = 0 it is observed that capacitor voltage has the value  $V_c = 0.5V$ . For the element values given, determine  $V_z$  (t) after converting the circuit into transformed domain. (14 marks)

#### **MODULE IV**

17 For the network, determine Driving point impedance  $Z_{11}(s)$ , Voltage gain Transfer function  $G_{21}(s)$  and Current gain Transfer function  $\alpha_{21}(s)$ . (14 marks)

18 Compare and contrast the necessary conditions for a network driving point function and Transfer functions. (7 marks)

b. For following network, evaluate the admittance function Y(s) as seen by the source i(t). Also pot the poles and zeros of Y(s). (7 marks)

#### **MODULE V**

19. a. Deduce the transmission parameters of two port network in terms of (i) Z-parameters,<br/>(ii) Y-parameters and (iii) Hybrid parameters.(10 marks)

b. How to determine the given two port network is Symmetrical (4 marks)

20 Two identical sections of the following networks are connected in parallel. Obtain the Y parameters of the combination. (14 marks)

| ECL201 | SCIENTIFIC COMPUTING | CATEGORY | L | T | P | CREDIT |

|--------|----------------------|----------|---|---|---|--------|

|        | LABORATORY           | PCC      | 0 | 0 | 3 | 2      |

#### **Preamble:**

- The following experiments are designed to translate the mathematical concepts into system design

- The students shall use Python for realizing experiments. Other softwares such as R/MATLAB/SCILAB/LabVIEW can also be used.

- The experiments will lay foundation for future labs such as DSP.

- The first two experiments are mandatory and any six of the rest should be done.

#### **Prerequisite:**

- MAT 101 Linear Algebra and Calculus

- MAT 102 Vector Calculus, Differential Equations and Transforms

Course Outcomes: After the completion of the course the student will be able to

| CO1 | Describe the needs and requirements of scientific computing and to<br>familiarize one programming language for scientific computing anddata<br>visualization. |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO2 | Approximate an array/matrix with matrix decomposition.                                                                                                        |

| CO3 | Implement numerical integration and differentiation.                                                                                                          |

| CO4 | Solve ordinary differential equations for engineering applications                                                                                            |

| CO5 | Compute with exported data from instruments                                                                                                                   |

| CO6 | Realize how periodic functions are constituted by sinusoids                                                                                                   |

| CO7 | Simulate random processes and understand their statistics.                                                                                                    |

#### Mapping of course outcomes with program outcomes

|            | <b>PO 1</b> | <b>PO 2</b> | <b>PO 3</b> | <b>PO 4</b> | <b>PO 5</b> | <b>PO 6</b> | <b>PO 7</b> | <b>PO 8</b> | <b>PO 9</b> | <b>PO10</b> | PO11 | <b>PO12</b> |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------|-------------|

| CO1        | 3           | 3           | 3           | 2           | 3           | 0           | 0           | 0           | 3           | 1           | 0    | 3           |

| CO2        | 3           | 3           | 1           | 2           | 3           | 0           | 0           | 0           | 3           | 0           | 0    | 1           |

| <b>CO3</b> | 3           | 3           | 1           | 1           | 3           | 0           | 0           | 0           | 0           | 0           | 0    | 1           |

| CO4        | 3           | 3           | 1           | 1           | 3           | 0           | 0           | 0           | 0           | 0           | 0    | 1           |

| CO5        | 3           | 3           | 1           | 3           | 0           | 0           | 0           | 0           | 3           | 3           | 0    | 0           |

| CO6        | 3           | 3           | 2           | 2           | 3           | 0           | 0           | 0           | 3           | 1           | 0    | 0           |

| <b>CO7</b> | 3           | 3           | 2           | 2           | 3           | 0           | 0           | 0           | 3           | 1           | 0    | 1           |

#### Assessment Pattern

Mark distribution

| Total Marks | CIE | ESE |

|-------------|-----|-----|

| 150         | 75  | 75  |

#### **Continuous Internal Evaluation Pattern:**

| Attribute                                                 | Mark |

|-----------------------------------------------------------|------|

| Attendance                                                | 15   |

| Continuous assessment                                     | 30   |

| Internal Test (Immediately before the second series test) | 30   |

End Semester Examination Pattern: The following guidelines should be followed regarding award of marks.

| Attribute                                              | Mark |

|--------------------------------------------------------|------|

| Preliminary work                                       | 15   |

| Implementing the work/Conducting the experiment        | 10   |

| Performance, result and inference (usage of equipments | 25   |

| and trouble shooting)                                  |      |

| Viva voce                                              | 20   |

| Record                                                 | 5    |

**General instructions:** End-semester practical examination is to be conducted immediately after the second series test covering entire syllabus given below. Evaluation is to be conducted under the equal responsibility of both the internal and external examiners. The number of candidates evaluated per day should not exceed 20. Students shall be allowed for the examination only on submitting the duly certified record. The external examiner shall endorse the record.

#### **Course Level Assessment Questions**

### CO1-The needs and requirements of scientific computing and to familiarize one programming language for scientific computing and data visualization

- 1. Write a function to compute the first *N* Fibonacci numbers. Run this code and test it.

- 2. Write a function to compute the sum of N complex numbers. Run this code and test it.

- 3. Write a function to compute th factorial of an integer. Run this code and test it.

#### CO2-Approximation an array/matrix with matrix decomposition.

- 1. Write a function to compute the eigen values of a real valuedmatrix (say 5 5). Run this code. Plot the eigen values and understand their variation.

- 2. Write a function to approximate a 5 5 matrix using its first 3 eigen vales. Run the code and compute the absolute square error in the approximation.

#### **CO3-Numerical Integration and Differentiation**

- 1. Write and execute a function to return the first and second derivative of the function  $f(t) = 3t^4 + 5$  for the vector t = [-3, 3].

- 2. Write and execute a function to return the value of  $\int_{-3}^{3} e^{-|t|} dt$

#### **CO4-Solution of ODE**

1. Write and execute a function to return the numerical solution of

$$\frac{d^2x}{dt^2} + 4\frac{dx}{dt} + 2x = e^{-t}\cos\left(t\right)$$

2. Write and execute a function to<sub>L</sub> solve for the current transient through an RL network (with r/L = 1) that is driven by the signal  $5e^{-t}U(t)$

#### **CO5-Data Analysis**

- 1. Connect a signal generator to a DSO and display a 1 V, 3 kHz signal. Store the trace in a usb device as a spreadsheet. Write and execute a function to load and display signal from the spreadsheet. Compute the rms value of the signal.

- 2. Write and execute a program to display random data in two dimensions as continuous and discrete plots.

#### **CO6-Convergence of Fourier Series**

1. Write the Fourier series of a traingular signal. Compute this sum for 10 and 50 terms respectively. Plot both signals on the same GUI.

#### **CO7-Simulation of Random Phenomena**

1. Write and execute a function to toss three fair coins simultaneously.Compute the probability of getting exactly two heads for 100 and 1000 number of tosses

#### Experiments

#### **Experiment 1. Familiarization of the Computing Tool**

- 1. Needs and requirements in scientific computing

- 2. Familiarization of a programming language like Python/R/ MATLAB/ SCILAB/ LabVIEW for scientific computing

- 3. Familiarization of data types in the language used.

- 4. Familiarization of the syntax of while, for, if statements.

- 5. Basic syntax and execution of small scripts.

#### **Experiment 2. Familiarization of Scientific Computing**

- 1. Functions with examples

- 2. Basic arithmetic functions such as abs, sine, real, imag, complex, sinc etc. using bulit in modules.

- 3. Vectorized computing without loops for fast scientific applications.

#### **Experiment 3. Realization of Arrays and Matrices**

- 1. Realize one dimensional array of real and complex numbers

- 2. Stem and continous plots of real arrays using matplotlib/GUIs/charts.

- 3. Realization of two dimensional arrays and matrices and their visualizations with imshow/ matshow/ charts

- 4. Inverse of a square matrix and the solution of the matrix equation $[\mathbf{A}][\mathbf{X}] = [\mathbf{b}]$  where  $\mathbf{A}$  is an  $N \times N$  matrix and  $\mathbf{X}$  and  $\mathbf{b}$  are  $N \times 1$  vectors.

- 5. Computation of the rank ( $\rho$ ) and eigen values ( $\lambda_i$ ) of **A**

- 6. Approximate A for N = 1000 with the help of singular value composition of A as  $A^{\sim} = \sum_{i=0}^{r} \lambda_i U_i V^T$  where  $U_i$  and  $V_i$  are the singular vectors and  $\lambda_i$  are the eigen values with  $\lambda_i < \lambda_j$  for i > j. One may use the built-in functions for singular value decomposition.

- 7. Plot the absolute error( $\zeta$ ) between **A** and  $\tilde{\mathbf{A}}$  as

$$\zeta = \sum_{i=1}^{N} \sum_{j=1}^{N} |a_{i,j} - a_{i,j}|^2$$

against r for r = 10, 50, 75, 100, 250, 500, 750 and appreciate the plot.

#### **Experiment 4. Numerical Differentiation and Integration**

- 1. Realize the functions sin t,  $\cos t$ , sinht and  $\cosh t$  for the vector t = [0; 10] with increment 0.01

- 2. Compute the first and second derivatives of these functions using built in tools such as grad.

- 3. Plot the derivatives over the respective functions and appreciate.

- 4. Familiarize the numerical integration tools in the language you use.

- 5. Realize the function  $f(t) = 4t^2 + 3$  and plot it for the vector t = [-5; 5] with increment 0.01

- Use general integration tool to compute  $\int_{-2}^{2} f(t)dt$ 6.

- Repeat the above steps with trapezoidal and Simpson method and compare the results. 7.

- Compute  $\frac{1}{\sqrt{2\pi}} \int_{0}^{\alpha} e^{\frac{-x^2}{2}} dx$ using the above three methods. 8.

#### **Experiment 5. Solution of Ordinary Differential Equations**

- Solve the first order differential equation  $\frac{dx}{dt} + 2x = 0$  with initial condition x(0) = 11.

- Solve for the current transient through an RC network (with RC = 3) that is driven by 2.

- 5 V DC 0

- the signal 5e<sup>-t</sup> U(t) and plot the solutions. Solve the second order differential equation  $\frac{d^2x}{dt^2} + 2\frac{dx}{dt} + 2x = e^{-t}$ 3.

- Solve the current transient through a series RLC circuit with  $R = 1 \Omega$ , L = 1 mH and  $C = 1 \mu$ 4. F that is driven by

- o 5 V DC

- the signal  $5e^{-t} U(t)$ .

#### **Experiment 6. Simple Data Visualization**

- Draw stem plots, line plots, box plots, bar plots and scatter plots with random data. 1.

- 2. plot the histogram of a random data.

- 3. create legends in plots.

- Realize a vector t = [-10; 10] with increment 0.01 as an array. 4.

- Implement and plot the functions 5.

- $\circ$  f(t) = cos t

- $f(t) = \cos t \cos 5t + \cos 5t$  $\cap$

#### **Experiment 7. Simple Data Analysis with Spreadsheets**

- Display an electrical signal on DSO and export it as a .csv file. 1.

- 2. Read this .csv or .xls file as an array and plot it.

- 3. Compute the mean and standard deviation of the signal. Plot its histogram with an appropriate bin size.

#### **Experiment 8. Convergence of Fourier Series**

The experiment aims to understand the lack of convergence of Fourier series

1. Realize the Fourier series

$f(t) = 4/\pi \left[ 1 - 1/3 \cos 2\pi 3t/T + 1/5 \cos 2\pi 5t/T - 1/7 \cos 2\pi 7t/T + \cdots \right]$

- 2. Realize the vector t = [0; 100] with an increment of 0.01 and keep T = 20.

- 3. Plot the first 3 or 4 terms on the same graphic window and understand how the smooth sinusoids add up to a discontinuous square function.

- 4. Compute and plot the series for the first 10, 20, 50 and 100 terms of the and understand the lack of convergence at the points of discontinuity.

- 5. With t made a zero vector, f(0) = 1, resulting in the Madhava series for  $\pi$  as

$$\pi = 4[1 - 1/3 + 1/5 - 1/7 + \cdots]$$

6. Use this to compute  $\pi$  for the first 10, 20, 50 and 100 terms.

#### **Experiment 9: Coin Toss and the Level Crossing Problem**

- 1. Simulate a coin toss that maps a head as 1 and tail as 0.

- 2. Toss the coin N = 100, 500,1000, 5000 and 500000 times and compute the probability (p) of head in each case.

- 3. Compute the absolute error |0.5 p| in each case and plot against N and understand the law of large numbers.

- 4. Create a uniform random vector with maximum magnitude 10, plot and observe.

- 5. Set a threshold (VT = 2) and count how many times the random function has crossed VT.

- 6. Count how many times the function has gone above and below the threshold.

Schedule of Experiments: Every experiment should be completed in three hours.

| ECL203 | LOGIC DESIGN LAB | CATEGORY L T P C | CREDIT |

|--------|------------------|------------------|--------|

|        |                  | PCC 0 0 3        | 2      |

#### **Preamble:**

This course aims to

- (i) familiarize students with the Digital Logic Design through the implementation of Logic Circuits using ICs of basic logic gates

- (ii) Familiarize students with the HDL based Digital Design Flow.

#### **Prerequisite:** Nil

Course Outcomes: After the completion of the course the student will be able to

| CO1 | Design and demonstrate the functioning of various combinational and sequential circuits using ICs |

|-----|---------------------------------------------------------------------------------------------------|

| CO2 | Apply an industry compatible hardware description language to implement digital circuits          |

| CO3 | Implement digital circuis on FPGA boards and connect external hardware to the boards              |

| CO4 | Function effectively as an individual and in a team to accomplish the given task                  |

# Mapping of course outcomes with program outcomes

|     | <b>PO 1</b> | <b>PO 2</b> | PO 3 | <b>PO 4</b> | <b>PO 5</b> | <b>PO 6</b> | <b>PO 7</b> | <b>PO 8</b> | <b>PO 9</b> | <b>PO10</b> | PO11 | PO12 |

|-----|-------------|-------------|------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------|------|

| CO1 | 3           | 3           | 3    |             |             |             |             |             | 3           |             |      | 3    |

| CO2 | 3           | 1           | 1    | 3           | 3           |             |             |             | 3           |             |      | 3    |

| CO3 | 3           | 1           | 1    | 3           | 3           |             |             |             | 3           | 1           |      | 3    |

| CO4 | 3           | 3           | 3    |             | 3           |             |             |             | 3           |             |      | 3    |

#### **Assessment Pattern**

#### Mark distribution

| Total Marks | CIE | ESE | ESE Duration |

|-------------|-----|-----|--------------|